OrFPGAN is an empirical performance optimization search tool that efficiently explores the “user tunable” parameter space of an FPGA design and assists in deducing the near optimal design in terms of timing score, device utilization, and power consumption. The tunable parameter space includes IPCore parameters and parameter settings for the vendor’s design tools.

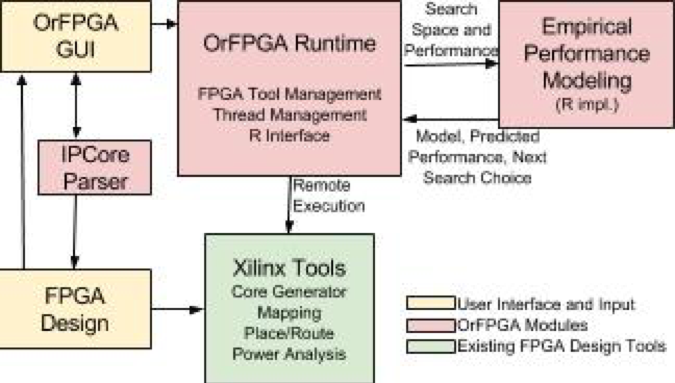

The user is able to input the IPCores parameters and design tools parameters through a custom built GUI. A parser interprets the FPGA design and user input, generates the parameter combinations, and generates a search space for OrFPGA. An empirical performance modeling module is responsible for generating performance models and performing a guided search of the space. The existing FPGA design tools (e.g., Xilinx FPGA design tools) are leveraged for generating the performance data for training instances. The tool leverages the parallel computing resources in emerging architectures for simultaneously executing multiple instances of the Xilinx FPGA design tools in order to reduce the turnaround tine and mitigate the long FPGA build time.

The methodology is able to reduces the power for designs that close and reduce the timing score for designs that do not close, when compared to the best-in-class search tools from Xilinx (i.e., SmartXplorer). The scope for FPGA Design improvement is highly dependent on the design and the extent to which the design is constrained.